### GROWTH, FABRICATION AND CHARACTERIZATION OF CARBON NANOTUBE BASED FIELD EFFECT TRANSISTORS

Claire McTaggart<sup>1,2</sup>, T. Ohya<sup>2</sup>, E. Maruyama<sup>2</sup>, A. Subagyo<sup>2</sup>, and K. Sueoka<sup>2</sup>

- 1. NanoJapan Program, Rice University and Department of Electrical Engineering, University at Buffalo, State University of New York

- 2. Graduate School of Information Science and Technology, Hokkaido University, Sapporo,

Japan

With favorable electrical and optical properties, carbon nanotube (CNT) based field effect transistors (FETs) are a promising area of nano-scale research. Compared to conventional MOSFETs, CNT-FETs can be used to create smaller, higher speed devices. However, due to the lack of precise control over CNT growth and the CNT's sensitivity to adhesive materials on the surface, it has been a difficult task to fabricate CNT-FETs with uniform electrical properties. Our experimental project consists of two parts. The first is to learn the basic micro-fabrication techniques used to make CNT-FETs with single-walled CNT channels. To make these samples, we used p-type silicon wafers with layers of SiO<sub>2</sub>. First, spin-coating was used to place two layers of resist on the substrate; the first to improve the bond between the substrate and the photo-resist and to prevent excess material from being deposited on the ends and then a layer of Through positive-type photolithography, the locations of the catalysts were photo-resist. patterned. Next, electron beam deposition was used to add the catalysts for CNT growth. Then, utilizing chemical vapor deposition, CNTs were grown. Following this, electron beam and thermal evaporation thin film deposition were used to place layers of Ti and Au on the substrate for use as electrodes. Finally, via atomic layer deposition, HfO<sub>2</sub> was deposited to add passivation and to decrease the hysteresis on the samples. For our measurement setup, we used a semiconductor parameter analyzer to measure current versus voltage and current versus ground voltage, for both source-drain and gate-drain applied voltages. In the second part of the project we will design CNT-FETs with suspended CNT channels. According to the design, electron beam lithography will be used to make the holes underneath the CNT channels and will be investigating appropriate conditions for the reactive ion etching process to make the hole. Electrical properties of the devices will be investigated in detail.

# Growth, Fabrication and Characterization of **Carbon Nanotube Based Field Effect Transistors**

Claire McTaggart<sup>1,2</sup>, T. Ohya<sup>2</sup>, E. Maruyama<sup>2</sup>, A. Subagyo<sup>2</sup>, and K. Sueoka<sup>2</sup>

1. NanoJapan Program, Rice University and Department of Electrical Engineering, University at Buffalo, State University of New York 2. Graduate School of Information Science and Technology, Hokkaido University, Sapporo, Japan

**Measurement Setup**

### Introduction

With favorable electrical and optical properties and their application to smaller, higher speed devices and sensors, carbon nanotube (CNT) based field effect transistors (FETs) are a promising area of nano-scale research.

Our experimental project was to first learn the basic micro-fabrication techniques needed to fabricate and evaluate FETs with single-walled CNT channels and then to fabricate CNT-FETs with self-suspended CNT channels. These devices will offer a unique opportunity to investigate the electro-optical properties of CNT channels without the effects of the adhesive materials' interaction with the channel on the substrate.

### **Future Plans**

In order to further study the electro-optical properties of the CNT-FETs, reactive ion etching will be used in combination with the above process to fabricate FETs with suspended CNTs as the channel. The appropriate conditions for the reactive ion etching process to make the hole and the electrical properties of the devices will de investigated in detail.

This material is based upon work supported by the National Science Foundation under Grant No. OISE-0530220.

## **Device Fabrication**

Electrode

CNT

HfO<sub>2</sub>

Si

- (1) Used Si wafers covered in  $SiO_2$ Si thickness: 500µm SiO<sub>2</sub> thickness: 300nm

- (2) Deposited catalysts for CNT growth Si(20nm) / Al(30nm) / Fe(2nm) / Mo(0.3nm)

- (3) CNT growth via chemical vapor deposition Growth temp: 900° C Growth time: 15 min Gases:  $CH_4$  (1000sccm) and  $H_2$  (500sccm)

- (4) Deposited electrodes Ti(20nm) / Au(60nm)

- (5) Deposited HfO<sub>2</sub> via atomic layer deposition Thickness: 20nm

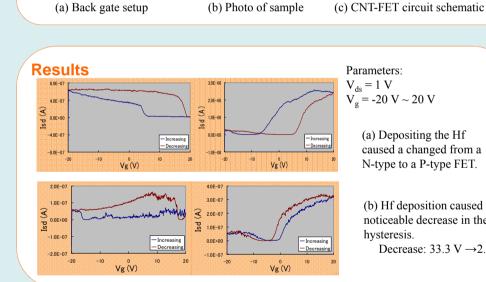

caused a changed from a N-type to a P-type FET.

CNTs

(b) Hf deposition caused a noticeable decrease in the Decrease: 33.3 V  $\rightarrow$  2.7 V